The rapid advancement of GaN technology has enabled the development of high-power, high-voltage, and high-frequency devices. This progress is particularly evident in the performance of GaN transistors, which now operate at unprecedented levels of efficiency and power density.

As illustrated in Figure 1, Qorvo’s QPD1013 transistor is built on a 0.50 μm GaN-on-SiC platform, offering excellent performance for RF applications. It is housed in a compact 6.6 x 7.2 mm DFN (Dual Flat No-lead) package, which simplifies PCB assembly compared to traditional cermet packages, making it more cost-effective for mass production.

Despite the high efficiency of Qorvo's GaN transistors, their operation at high RF power levels still leads to significant power consumption. Since these are surface-mount components, careful PCB layout is essential to ensure optimal thermal management. Both copper via arrays and copper coin technologies have been evaluated for heat dissipation, with results showing that both methods can improve thermal performance effectively.

The first approach involves using an array of copper-plated vias beneath the ground pad of the transistor, enhancing heat transfer from the device to the PCB. The second method uses copper coins—solid copper blocks embedded in the PCB during manufacturing—to provide a direct thermal path to the board's carrier. While many manufacturers are familiar with copper-clad technology, copper coin implementation at RF frequencies is still evolving and not yet fully mature.

Transistor Measurement

In this design, large and small signal measurements were conducted on sample transistors mounted on a 20-mil thick Rogers RO4350 substrate. The transistor was biased at 65V and 240mA under static conditions.

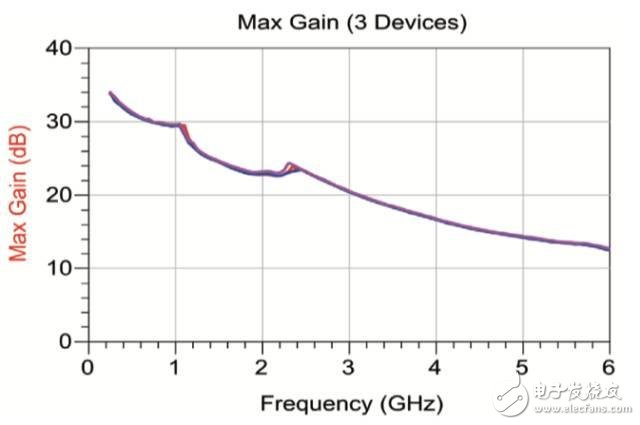

Figure 2 displays the maximum usable gain (MAG) of three different transistors across various frequencies, demonstrating good uniformity between devices. Although the QPD1013 achieves a gain above 6 GHz, it is typically optimized for operation up to around 3.5 GHz due to practical design considerations.

Maximum Gain (3 Devices) | Maximum Gain (dB) | Frequency (GHz)

Load pull measurements indicate that when operating at a 10% duty cycle with a 100 μs pulse width, the transistor can deliver over 52 dBm (160 W) of RF output power with approximately 70% efficiency. This data serves as the foundation for the power amplifier’s large-signal design.

Power Amplifier Design

The design of the power amplifier begins with ensuring that the transistor remains unconditionally stable across the entire operating frequency band. Stability is achieved by incorporating an RC network at the RF input. Due to the high power consumption of conventional SMT resistors, high-power aluminum nitride resistors from IMS are used instead. The amplifier must remain stable at temperatures as low as -40°C to support wide temperature operation. Adding appropriate RC decoupling at the bias feed point significantly improves low-band stability, and this can be implemented later in the design process.

Using initial load pull data provided by Qorvo, the optimal load impedance for maximizing output power and drain efficiency between 1.2 GHz and 1.8 GHz was determined. Under specific load conditions, the QPD1013 can deliver up to 200W, but careful attention must be given to operating efficiency to maintain acceptable junction temperatures. The load impedance that yields the highest drain efficiency is selected as the target for the output matching network, ensuring both high RF output power and efficient thermal performance.

The output matching network employs a bandpass topology to achieve the desired load impedance. High operating voltages and RF power levels require careful design to prevent overheating or damage. The RF traces must be sufficiently wide to handle the power without excessive heating. Matching capacitors must also be chosen carefully to withstand both DC and RF voltage swings while maintaining a high Q value to minimize power loss and maintain efficiency.

Keysight Momentum is used for planar electromagnetic simulations of the metal parts in the output matching network, and multi-port S-parameter blocks are simulated using the high-frequency model of the O805 SMT component. Figure 3 shows a hybrid EM/schematic diagram of the output matching network.

The simulated load impedance is plotted against the target on a Smith chart normalized to 10 Ω in Figure 4. The simulated curve overlays the provided load pull profile, confirming that the target power and efficiency levels will be met.

S(3,3) QPD1013_Opt_Zload_v1..S(1,1)

Frequency (1.200GHz to 1.9000GHz)

The analog insertion loss of the output network is shown in Figure 5.

The loss in the output matching network comes from transmission line losses and SMT component losses within the PCB material. At these high power levels, even a small fraction of a dB of loss can result in several watts of power dissipation, significantly reducing overall PA efficiency.

Figure 6: EM Analog Input Matching

The input matching network utilizes a low-pass architecture. Aluminum nitride resistors from IMS are used in the gate stability network, capable of handling several watts of power. This allows the PA to withstand high input drive levels of 10–20W required for P-3dB compression. Figure 6 illustrates the input matching network similarly to the output network.

The layout of the input and output matching networks includes inductive loops and pads for post-manufacturing tuning. However, in the final design, only minor adjustments to the capacitance values were necessary.

The analog small signal performance of the PA is shown in Figure 7, illustrating a wide bandwidth and flat gain response across the frequency range.

A solar cell panel, solar electric panel, photo-voltaic (PV) module, PV panel or solar panel is an assembly of photovoltaic solar cells mounted in a (usually rectangular) frame, and a neatly organised collection of PV panels is called a photovoltaic system or solar array. Solar panels capture sunlight as a source of radiant energy, which is converted into electric energy in the form of direct current (DC) electricity. Arrays of a photovoltaic system can be used to generate solar electricity that supplies electrical equipment directly, or feeds power back into an alternate current (AC) grid via an inverter system.

Solar Panel,200w Folding Solar Panel,Folding Solar Portable Power Station,Sunpower Solar Cell

suzhou whaylan new energy technology co., ltd , https://www.xinlingvideo.com