Through the previous PL DMA design, it was normal to run in the SDK. However, there were some issues with the block design and source design that required manual correction. After fixing the obvious errors, the system could generate a bit file for SDK debugging.

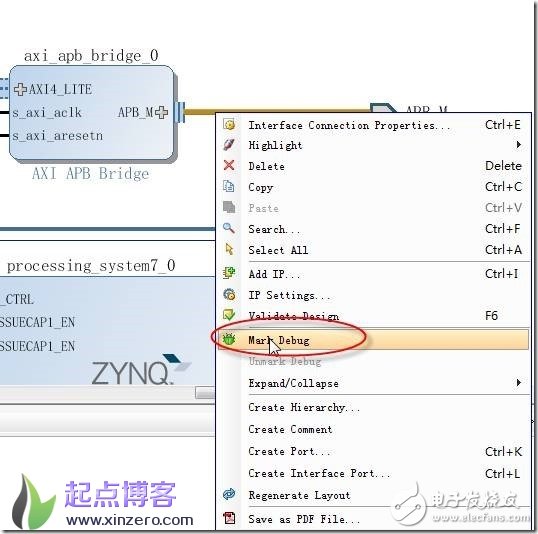

The first step in debugging was to focus on the PL section, which is controlled by the APB bus. I marked this section for debugging as shown below.

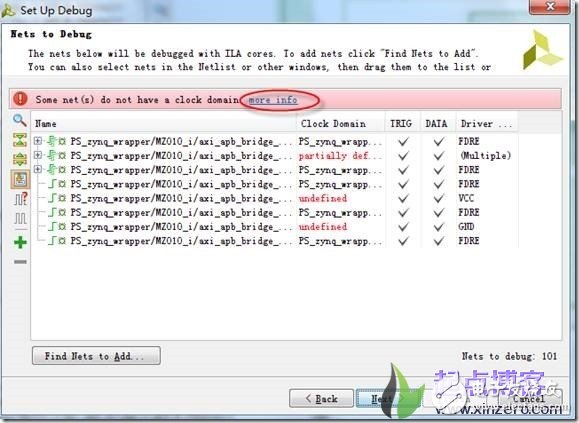

After re-synthesizing and completing the comprehensive build, I did not proceed with implementation. Instead, I went to the “Set Up Debug†option under the integrated menu and configured the ILA. The following settings window appeared.

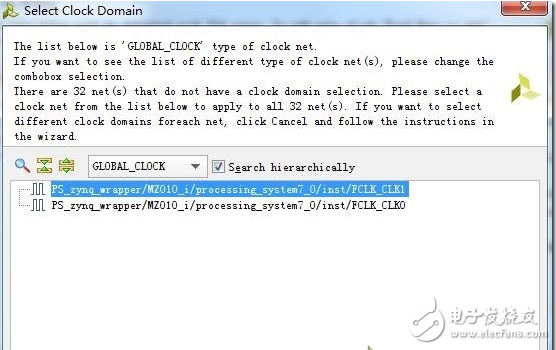

Clicking “More Info†showed a warning that some netlists had no clock set. I selected all of them and right-clicked to assign the clock, as shown below.

I chose FCLK_CLK1, which runs at 150MHz, because the APB bus uses FCLK_CLK0 at 50MHz. A 150MHz clock was suitable for sampling, and the default settings worked well. Then, I generated the bit file.

Debugging Process

First, I started the test program for the PL DMA PS part in the SDK and stopped it at the main function.

Then, I opened the ILA debug window in Vivado.

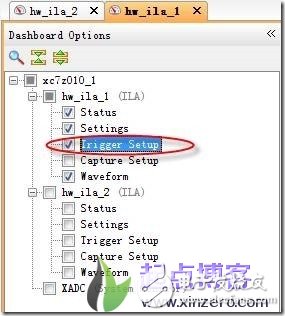

In the ILA window, I selected “Trigger Setup†to configure the trigger conditions.

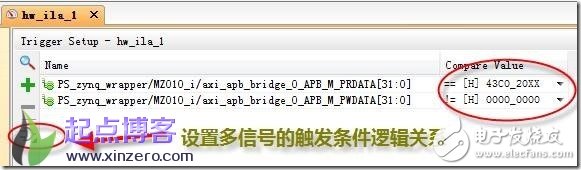

In the Trigger Setup window, I added multiple signals using the “+†button and set the trigger condition based on the Compare Value. For multiple conditions, I used logical operators on the left side.

I selected the trigger condition as shown in the image above.

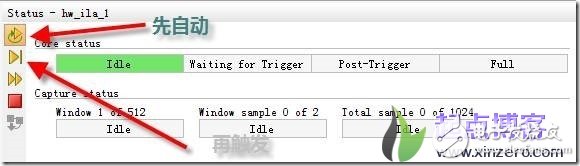

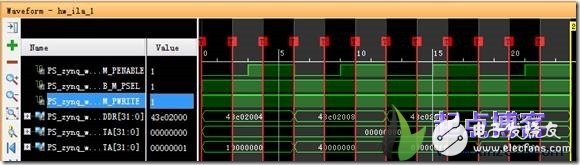

Then, I ran the test in the SDK. After reading the address space corresponding to the APB bus, the debug window displayed the following information.

The data from the APB bus matched the data written from the PS side, confirming that everything was working correctly.

The Projector metal hanger is flexible and suitable for various models.

Projector Mount,Projector Stand,Projector Holder,Projector Screen Holder

Jiangsu D-Bees Smart Home Co., Ltd. , https://www.cI-hometheater.com