Through the previous PL DMA design, when running in the SDK, it was normal that it didn’t run initially. The block design and source design were created manually, and any obvious errors had been fixed. A bit file could be generated for SDK debugging.

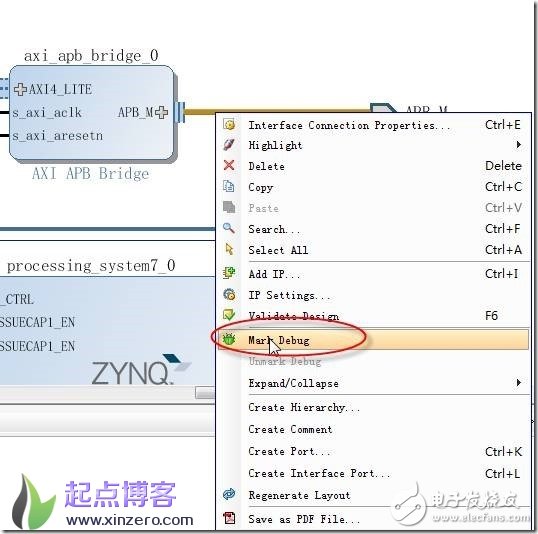

The first step in debugging focused on the PL section since the PL DMA controls the APB bus. I marked it for debugging as shown below.

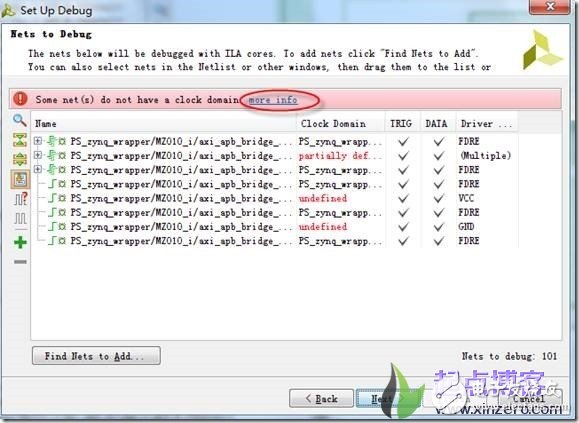

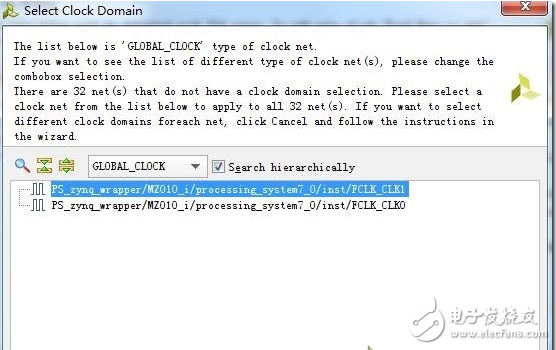

After re-synthesizing and completing the synthesis, I skipped the implementation phase. Then, under the "Set Up Debug" option in the menu, I configured the ILA. The following configuration window appeared.

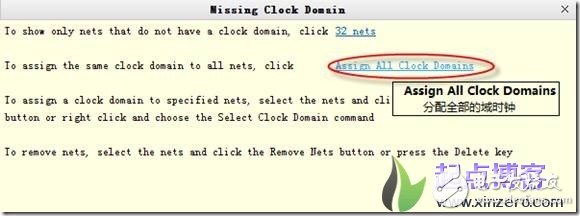

Clicking “More Info†showed a warning that some netlists did not have a clock assigned.

I selected all signals, right-clicked, and chose the clock. As shown below, I selected FCLK_CLK1, which runs at 150MHz, while the APB bus uses FCLK_CLK0 at 50MHz. Using a faster clock made it easier to sample the signal.

After setting the clock, I generated the bit file. Next, I started the test program for the PL DMA in the SDK and paused it at the main function.

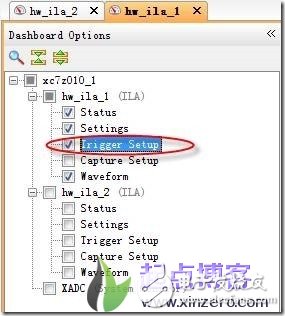

Then, I opened the ILA debug window in Vivado.

In the ILA window, I selected “Trigger Setup†to configure the trigger conditions.

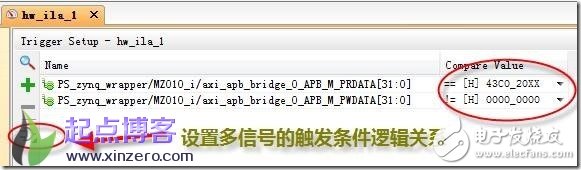

Using the “+†button, I added multiple signals to monitor and set the trigger condition using the Compare Value. For multiple conditions, I adjusted the logical relationships on the left side of the window.

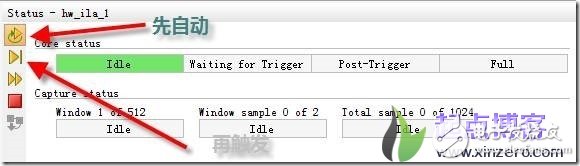

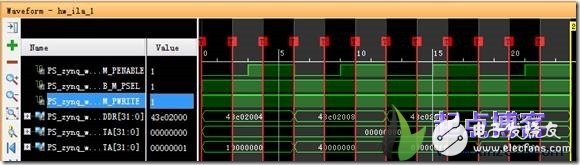

After selecting the trigger condition, I ran the test program in the SDK. Once the address space corresponding to the APB bus was read, the ILA debug window displayed the following information.

By comparing the data shown in the figure with the data written from the PS side, I confirmed that the APB bus was functioning correctly. This process helped identify and resolve potential issues during the PL DMA communication.

Tubular motor with stable output and dust-proof sealing design, making the screen longer and safer to use. The screen lifting is smooth and does not get stuck, with high performance and low consumption.

Electric Projection Screen,Motorized Projector Screen,Outdoor Motorized Projector Screen,Home Projector Screen

Jiangsu D-Bees Smart Home Co., Ltd. , https://www.cI-hometheater.com