1. Introduction

With the rapid advancement of information technology, the real-time collection and processing of various types of data have become essential in modern industrial control and scientific research, especially in fields such as high-speed signal measurement, image processing, and audio signal analysis. To meet these demands, high-performance data acquisition systems are required. This leads to two main design requirements for such devices: first, the interface must be simple, flexible, and capable of high-speed data transmission; second, since large volumes of data are typically involved, the host system must respond quickly and perform real-time analysis and processing.

In software-defined radio (SDR) architectures, digital down conversion (DDC) plays a crucial role and is considered one of the core technologies. After analog-to-digital conversion (ADC), DDC processes high-speed and high-capacity data, making its implementation challenging. To address this challenge and meet the two key requirements of data acquisition systems, this report proposes a data acquisition and real-time transmission scheme based on FPGA and USB 2.0 technology.

The system described in this paper utilizes a Spartan-6-based high-speed data acquisition, processing, and real-time transmission setup. It aims to extract high-speed orthogonal IQ data from a broadband IF digital receiver and send it to the FPGA for subsequent signal processing in software radio applications. The Cypress EZ-USB FX2 is used for high-speed data transmission, either for baseband data or data processed by the FPGA. Host computer software is then used to store and display the received data. This paper covers three main aspects: the high-speed data acquisition module (wideband IF digital down-conversion module), the high-speed data transmission module, and the host computer software, with both hardware and software designs discussed.

2. System Overview

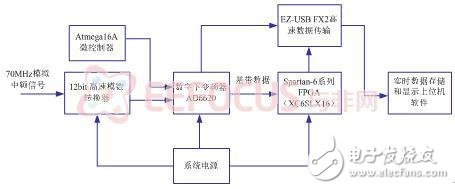

The entire system is divided into three sub-modules: (1) the high-speed data acquisition module (wideband IF digital down-conversion module); (2) the high-speed real-time processing and transmission module; and (3) the upper computer software module. A block diagram of the system is shown in Figure 1:

Figure 1: System overall principle block diagram

The high-speed data acquisition and EZ-USB data transmission modules are composed of corresponding hardware circuits and software. The PC software module is primarily developed using MFC with Microsoft Visual Studio 2008. The overall hardware block diagram is shown in Figure 2:

Figure 2: System hardware block diagram

The working principle of the system begins with the high-speed data acquisition module, which performs analog-to-digital conversion on a 70MHz IF analog signal at a sampling rate of 60MHz, following the bandpass sampling theorem. An Atmel Atmega16A microcontroller controls the process asynchronously, enabling special digital down-conversion to shift the 70MHz intermediate frequency signal to the baseband. The resulting baseband data rate remains at 60MHz, so the high-speed digital baseband signal needs to be extracted and filtered to obtain a low-speed baseband signal. The extraction factor can be programmed, and the lower the factor, the slower the baseband signal becomes. This low-speed baseband data is then sent to the FPGA for symbol recovery and information retrieval. The EZ-USB FX2 facilitates real-time data acquisition and transmission of the baseband signal and the output from the FPGA. Finally, the data is transferred to the host computer via a USB 2.0 interface for storage and real-time visualization.

3. High-Speed Data Acquisition Module (Wideband IF Digital Down-Conversion Module)

Traditional data acquisition systems often rely on microcontrollers or digital signal processors (DSPs) to control ADCs, memory, and other peripheral components. However, due to limitations in the MCU's instruction cycle and processing speed, clock frequencies are generally low. All functions must be implemented through software, leading to long execution times that reduce efficiency and make it difficult to meet real-time and synchronization requirements. While DSP-based systems offer faster processing, they come with higher costs and frequent interruptions that can degrade CPU performance and response time.

In recent years, FPGA-based data acquisition solutions have gained popularity due to their unique advantages. One of the most significant benefits is the ability to perform parallel data processing. Additionally, FPGAs offer short development cycles, high integration, low power consumption, high operating frequencies, cost-effective design, and flexible programming configurations. The high-speed data acquisition and real-time transmission system proposed in this report includes three key parts: (1) high-speed data acquisition and digital down-conversion processing, (2) high-speed data transmission, and (3) the upper computer data acquisition control section. The system first digitizes external analog signals, buffers the high-speed digital output from the ADC, transfers the buffered data to the FPGA after digital down-conversion, and uses the FPGA to control the CY7C68013A chip for high-speed real-time data transmission, storage, and display.

Photovoltaic Carport Structure

Photovoltaic Carport Structure,Solar Carport Mounting Structure System,Carport Mounting Structure System,Solar Energy System Metal Carports

Hebei Shuobiao New Energy Technology Co., Ltd. , https://www.pvbracketsystem.com